| (7 pages)                          | Reg. No.:                                                      |

|------------------------------------|----------------------------------------------------------------|

| Code No.: 6385                     | Sub. Code: ZPHM 13                                             |

|                                    | EGREE EXAMINATION,<br>EMBER 2022.                              |

| Fir                                | est Semester                                                   |

| Ph                                 | ysics – Core                                                   |

| INTEGRAT                           | TED ELECTRONICS                                                |

| (For those who jo                  | ined in July 2021 onwards)                                     |

| Time: Three hours                  | Maximum : 75 marks                                             |

|                                    | - (10 × 1 = 10 marks)<br>r ALL questions.                      |

| Choose the correc                  | t answer:                                                      |

| 1. In the satur characteristics of | ration region the I <sub>D</sub> -V <sub>GS</sub> a MOSFET are |

| (a) Linear                         | (b) Quadratic                                                  |

| (c) Exponential                    | (d) Hyberbolic                                                 |

| 2. In reverse biase                | ed condition SCR behaves as                                    |

Diode

JFET

(b) Transistor

(d) MOSFET

| 3. | If propagation delay time tp = 10 ns the output | ts |

|----|-------------------------------------------------|----|

|    | change approximately — after the arriva         | al |

|    | of the clock signal.                            |    |

|    | () 15                                           |    |

- (a) 20 ns

- (b) 15 ns

- (c) 10 ns

- (d) 5 ns

- 4. The circuit responds only where the clock is transaction between its two voltage states

- (a) RC triggering

- (b) Level triggering

- (c) Edge triggering

- (d) None

- Given a choice, integrators are almost invariably preferred over differentiators in analog circuits because

- (a) differentiators cause more noise at the output

- (b) differentiators don't allow frequency signals to pass

- (c) integrators are more immune to low frequency noise

- (d) the gain of a differentiator increases with frequency and therefore they are difficult to stabilize with respect to spurious oscillations

Page 2 Code No.: 6385

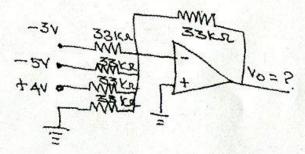

6. What is the expected output voltage in the following circuit?

(a) +2V

(b) -2V

(c) +4V

- (d) -4V

- 7. Monostable multivibrator circuit is sometimes called as ———— multivibrator.

- (a) free running

- (b) one shot

- (c) neither free running nor one shot

- (d) none

- - (a) 8.81

(b) 7.81

(c) 6.81

(d) 5.81

Page 3 Code No.: 6385

- - (a) Electric

- (b) Magnetic

- (c) Electro-magnetic

- (d) Coloumb

- 10. Signal conditioning often requires the signal to be filtered and isolated to remove unwanted back ground noise.

- (a) Output

- (b) Input

- (c) Neither input and output

- (d) None

PART B —

$$(5 \times 5 = 25 \text{ marks})$$

Answer ALL questions, choosing either (a) or (b).

11. (a) Explain the operation of enhancement MOSFET with diagram.

Or

(b) A 100  $\mu$  m thick silicon wafer has been doped uniformly with Boron of concentration  $\frac{10^{16}}{\text{cm}^3}$ . Find its sheet resistance. Given that for a p-type wafer y is given to be 100  $\mu$ m and hole mobility in a silicon is 500 cm²/V-S.

Page 4 Code No.: 6385 [P.T.O.]

12. (a) What does D-Flip flop do? Explain how JK flip-flop can be converted into D-Flip-flop with diagram and truth table.

Or

- (b) Draw the circuit of the integrated DTL gate and explain its operation for positive logic.

- 13. (a) Explain the action of voltage to current converter using Op-Amp.

Or

- (b) Draw the circuit of an Op-Amp differentiator and explain its operation.

- 14. (a) Draw the internal block diagram of the 555 chip and explain.

Or

- (b) Discuss the application of PLL IC for frequency multiplication.

- 15. (a) Write short notes on electric field shielding.

Or

(b) Explain the DC signal conditioning system with the help of block diagram.

Page 5 Code No.: 6385

PART C —  $(5 \times 8 = 40 \text{ marks})$

Answer ALL questions choosing either (a) or (b).

16. (a) List and explain the steps involved in fabricating a monolithic Integrated Circuit (IC) assuming already have a substrate.

Or

- (b) Explain the construction and VI characteristics of the Silicon Controlled Rectifier (SCR) as a function of Gate current.

- 17. (a) Explain the action of JK flip-flop with neat circuit diagram. Also explain, what is meant by race around condition in connection with JK flip-flop.

Or

- (b) Explain the action of a 4 bit ripple counter with circuit diagram and truth table. Also sketch the output waveforms.

- 18. (a) Sketch the simple hold circuit and explain its operation.

Or

(b) What are the desirable characteristics of instrumentation amplifier and explain its operation with circuit diagram?

Page 6 Code No.: 6385

Explain the action of IC voltage controlled 19. oscillator using IC 566 with block diagram and circuit diagram.

Or

- Explain the process of FSK demodulation using PLL.

- Write the principle of lock in amplifier. 20. Explain the lock in amplifier with block diagram. Also explain the sensitivity of lock in amplifier.

Or

Define noise with reference to electrical system. Classify and explain the noise sources.